<th id="2d88k"></th>

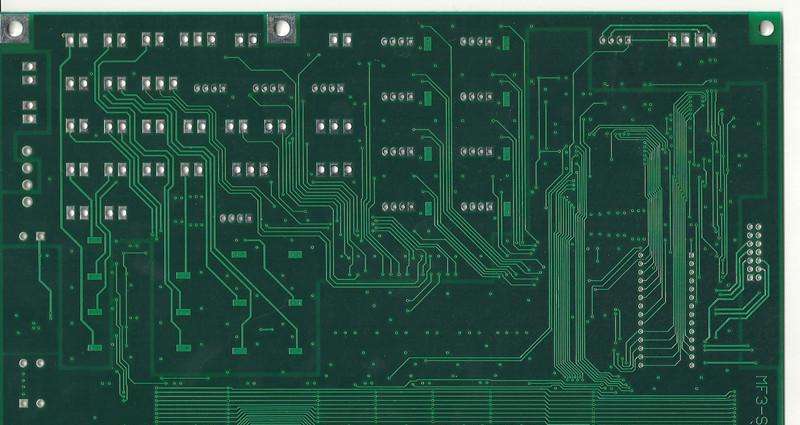

大家在看到一個pcb成品時,內(nèi)心是不是充滿著自豪呢?是不是覺得人類的智慧特別偉大呢?其時有這樣的想法都是正常的,畢竟pcb的出現(xiàn)無疑是一件十分棒的事情。但是在利用它之前,大家是否知道它的出現(xiàn)不是一瞬間的,相反它需要經(jīng)過pcb設(shè)計(jì)才可以得出來。同樣,專業(yè)的設(shè)計(jì)師在針對pcb設(shè)計(jì)的過程中會注意細(xì)節(jié)的方方面面,只有嚴(yán)格把關(guān)好這些細(xì)節(jié)上的事項(xiàng),只有合理地進(jìn)行布線連接才可以順順利利的讓電路板騰空出世。

下面的內(nèi)容是東莞市博遠(yuǎn)電子有限公司針對pcb設(shè)計(jì)的一些經(jīng)驗(yàn)分享,希望對有需求的人提供一些幫助:

首先,pcb設(shè)計(jì)師不是只會設(shè)計(jì)的,他們需要掌握的知識有很多,至少要十分了解各類電子元器年的工作原時,只有了解它們,只有知道它們彼此之間的關(guān)聯(lián),只有了解它們之間的影響,才能夠更加清楚地知道輸入與輸出的傳輸標(biāo)準(zhǔn),而且任何優(yōu)秀成功的電子產(chǎn)品都是以原理圖作為依托的,所以pcb設(shè)計(jì)師對版圖技術(shù)了解到位,才能夠避免后續(xù)工作中發(fā)生重大問題。

然后,pcb設(shè)計(jì)過程中的噪聲處理也迫在眉睫。目前要解決噪聲問題,那么就需要從三個方向入手。振鈴和串?dāng)_的問題,特別是一些關(guān)鍵性的信號要注意下串?dāng)_事項(xiàng),合理地運(yùn)用好差分信號,走線時利用好差分對走線,才可以從根本上消除感應(yīng)的問題,并且保證路徑的順利進(jìn)行,避免發(fā)生反彈的噪聲等等;pcb設(shè)計(jì)過程中,阻抗匹配度也是個要把關(guān)起來的問題,這一點(diǎn)是無比重要的,畢竟很多時間兩根線間的走線還是十分靠近的,所以pcb設(shè)計(jì)師們需要事先同廠家商定好使用怎樣的阻抗才行;pcb設(shè)計(jì)過程中的電容使用事項(xiàng),合理采用一下去耦電容器更有助于減小線路板的電源和地平面之間的電感,只有盡量控制好這點(diǎn)才可以保障后面工作的順利。

其次,pcb設(shè)計(jì)的過程中十分有可能會經(jīng)受著時鐘信號干擾的相關(guān)問題,大抵上的原因還是鐘線過分長千萬的,所以pcb設(shè)計(jì)的過程中需要避免使用多個層來傳輸時鐘,并且不要在時鐘線上有過孔,因?yàn)檫^孔將增加走線的阻抗變化和信號的反射。其次,如果必須用內(nèi)層來布設(shè)時鐘,那么上下層應(yīng)該使用地平面來減小延遲。再次,如果電源平面上不幸引入時鐘噪聲會增加PLL抖動,那么在修改PCB設(shè)計(jì)時可以創(chuàng)建一個“電源島”,這種技術(shù)可以利用金屬平面中的較厚蝕刻來實(shí)現(xiàn)PLL模擬電源和數(shù)字電源的隔離。

最后一點(diǎn),東莞市博遠(yuǎn)電子有限公司的工程師要講的是有關(guān)于pcb設(shè)計(jì)時的布局問題,大家都了解到pcb設(shè)計(jì)過程中最關(guān)鍵的還是連接,只有選擇恰當(dāng)?shù)摹⒅苯拥穆窂剑拍軌蚴斋@更好的效果,而這方面知識的掌握可以獲得更大的快樂,那么為什么不重視起來呢!

<th id="2d88k"></th>